#### الجمهورية الجزائرية الديمقراطية الشعبية

République Algérienne Démocratique et Populaire Ministère de l'enseignement Supérieur et de la recherche scientifique

Université Mohamed Khider Biskra Faculté des Sciences et de la Technologie Département de Génie Electrique Filière : Electronique

**Option: Micro-informatique et Instrumentation**

Réf: .../2010

Mémoire de Fin d'Etudes En vue d'obtention de diplôme: Master en électronique

# Thème

### ETUDE ET REALISATION D'UN PROGRAMMATEUR DE CARTE A PUCE ET SON LECTEUR

Présentée par : SELMI SYFEDDINE SEGHIR SALAH Proposé et Dirigé par :

Mr. ABDESSELAM SALIM

**PROMOTION 2009/2010**

#### الجمهورية الجزائرية الديمقراطية الشعبية

République Algérienne Démocratique et Populaire Ministère de l'enseignement Supérieur et de la recherche scientifique

Université Mohamed Khider Biskra Faculté des Sciences et de la Technologie Département de Génie Electrique Filière : Electronique

**Option:** Micro-informatique et Instrumentation

### Mémoire de Fin d'Etudes En vue d'obtention de diplôme: Master en électronique

## Thème:

### ETUDE ET REALISATION D'UN PROGRAMMATEUR DE CARTE A PUCE ET SON LECTEUR

| Présenté par :                                         |                       |

|--------------------------------------------------------|-----------------------|

| SELMI SYFEDDINE                                        |                       |

| SEGHIR SALAH                                           |                       |

| Avis favorable du président du Jury :<br>l'encadreur : | Avis favorable de     |

| Nom et prénom                                          | Mr. ABDESSELAM SALIM. |

|                                                        | Signature             |

Cachet et signature

### Résumé du mémoire de fin d'étude En vue d'obtention de diplôme: Master en électronique

**Option:** Micro-informatique et Instrumentation

# Thème:

### ETUDE ET REALISATION D'UN PROGRAMMATEUR DE CARTE A PUCE ET SON LECTEUR

Proposé par : Mr. ABDESSELAM SALIM

Dirigé par : Mr. ABDESSELAM SALIM

#### **RESUME**

La carte à puce est un nouveau « sésame » dans le monde des électroniciens, elle intervient dans plusieurs applications sensibles tel que les cartes bancaires, carte santé, carte Télévision à péage et le contrôle d'accès sécurisé.

On conclut dans ce mémoire l'étude et la réalisation d'un programmateur de carte à puce et son lecteur.

# Remerciement

Nous remercions Allah le tout puissant de nous avoir donné le courage, la volonté, la santé et surtout la patience, pour pouvoir, durant toutes ces longues années d'études, d'arriver la ou nous sommes aujourd'hui et d'exploiter tous nos efforts pour ce modeste travail.

Nous voudrions d'abord exprimer notre profonde reconnaissance à  $\mathcal{M}^{er}$  ABDESSELAM.S notre encadreur de thèse pour nous avoir encadré durant cette année, il a guidée efficacement nos travaux. Nous le remercions pour sa disponibilité et pour les conservations régulières sur ce travail, ses conseils scientifiques et techniques.

Aussi nous remercions les employeurs de laboratoire d'électronique surtout :

$\mathcal{M}^{er}$ , HAMZA.

Nous également remercions les membres du jury.

Finalement nous remercions toutes les personnes, qui de prés ou de loin, par leur compréhension leur coopération nous ont facilités la tâche et ont contribués à la mise en forme du thème.

### Dédicace

Je dédie ce travail qui est complété par l'aide de Dieu.

La prunelle de nos yeux, ceux qui nous éclairés le chemin de la réussite à nos parents que dieu les garde.

Je tiens aussi à dédier ce travail

A mes sœurs et mon frère Salem pour leur soutien.

A mes chers amis: Riad, Belkacem chikh, Okba, Houari, Fares, Fethi remli, Feth Zidane, Amor baa, Zohir benziadi, Lazhar, Abdelhakim, Amine chalhoub, chikh sofienne, Abdelhakim Amri, Isam, Mostapha, et hachouf ammar.

A tous mes collègues de sciences et techniques surtout d'option de

Micro-informatique et Instrumentation.

A toute personne de qui m'aide loin ou un autre.

Enfin, avec toute ma gratitude, je le dédie à la plus tendre et merveilleuse mère de tout les algériens et algériennes : Notre chère

Algérie.

Salah.

### Dédicace

Je dédie ce travail qui est complété par l'aide de Dieu.

La prunelle de nos yeux, ceux qui nous éclairés le chemin de la réussite à nos parents que dieu les garde.

Je tiens aussi à dédier ce travail

A mes sœurs et mes frères Ali, Chaanbane, Elhedi et Abd elrahim pour leur soutien.

A mes chers Amis: salaheddine, lakhder, Mohamed, khaled, hichem, imadeddine, dinar, Adel.

Fethi, Yazide, fika, walid, Wail, Josef, ramzi, hatem, sohaib, fares, kameleddine Choiki, bd torki, hassane, islame, issa, Nessereddine, Samire, Soufyane, toufa.

A tous mes collègues de électronique surtout d'option de micro-informatique et instrumentation et a tous les étudiants de la promotion.2<sup>eme</sup> Master des autres spécialités.

A toute personne de qui m'aide loin ou un autre.

Enfin, avec toute ma gratitude, je le dédie à la plus tendre et merveilleuse mère de tout les algériens et algériennes : Notre chère

Algérie.

Seyfeddine.

# **SOMMAIRE**

### Introduction générale.

### ETUDE THEORIQUE

### CHAPITRE I : Les cartes à puce.

| I.1. Introduction                                  | 1 |

|----------------------------------------------------|---|

| I.2. Généralités                                   | 1 |

| I.2.1. Définition de la carte à puce               | 1 |

| I.2.2. Classification des cartes à puces           | 1 |

| I.2.3.a. A base de ces composants                  | 1 |

| a1 : La carte à mémoire                            | 1 |

| a2 : La carte à microcontrôleur                    | 1 |

| I.2.3.b. A base de son interface                   | 2 |

| b1: La carte à contact                             | 2 |

| b2: La carte sans contact                          | 2 |

| b3: La carte combi ou carte hybride                | 2 |

| I.2.2.c. A base de système d'exploitation utilisée | 2 |

| I.2.3. Positionnement des contacts                 | 3 |

| <b>1.2.4.</b> Norme ISO 7816                       | 3 |

| <b>1.2.4.a.</b> Norme ISO7816-1                    | 3 |

| <b>1.2.4.b.</b> Norme ISO7816-2                    | 4 |

| 1.2.4.c. Norme ISO 7816-3                          | 5 |

| <b>1.2.4.d.</b> Norme ISO 7816-4                   | 6 |

| <b>1.2.4.e.</b> Norme ISO 7816-5                   | 6 |

| <b>1.2.4.f.</b> Norme ISO 7816-6                   | 6 |

| <b>1.2.4.g.</b> Norme ISO 7816-7                   | 6 |

| <b>1.2.4.h.</b> Norme ISO 7816-8                   | 7 |

| I.2.5. Spécification de la norme ISO 7816          | 7 |

| <b>1.2.6.</b> Les commandes ISO 7816               | 7 |

| I.2.7. Le protocole d'échange d'informations       | 8 |

| I.2.8. Les liaisons asynchrones                    | 8 |

| I.2.9. Avantage de la carte à puce                 | 9 |

| I.2.9.a. Au niveau physique                          | 9               |

|------------------------------------------------------|-----------------|

| I.2.9.b. Au niveau hardware                          |                 |

| I.2.9.c. Au niveau software                          |                 |

| I.2.10. Application des cartes à puces               |                 |

| I.3. Carte GOLD                                      | 11              |

| I.4. Carte SILVER                                    | 12              |

| I.5. Programmateur de carte à puce                   |                 |

| I.6. Lecteur carte à puce                            | 14              |

| I.7. La communication entre le lecteur et la carte   |                 |

| Conclusion                                           | 15              |

| CHAPITRE II : Les microcontrôleurs (PI               | C) et mémoires. |

| II.1. Introduction                                   | 16              |

| II.2. Généralités                                    | 17              |

| <b>II.3.</b> PIC 16F84                               |                 |

| II.3.1.brochage et fonction des pattes               | 20              |

| II.3.2. Architecture générale                        | 21              |

| II.3.3. Organisation de la mémoire                   | 22              |

| II.3.3.a. Mémoire de programme                       | 22              |

| II.3.3.b. Mémoire de données                         | 23              |

| <b>b1</b> : Registres généraux                       | 24              |

| <b>b2 :</b> Registres spéciaux–SFRs                  | 24              |

| <b>b3</b> : Mémoire EEPROM                           | 25              |

| II.3.4. Jeu d'instructions                           | 25              |

| II.3.4.a. Format général                             | 26              |

| II.3.4.b. Exemple d'instruction—le transfert         | 26              |

| II.3.4.c. Liste des instructions                     | 29              |

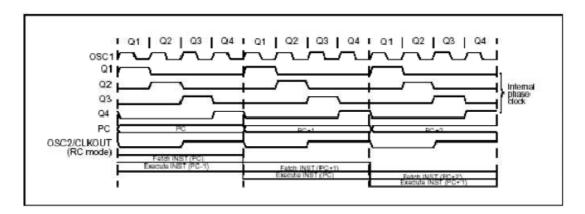

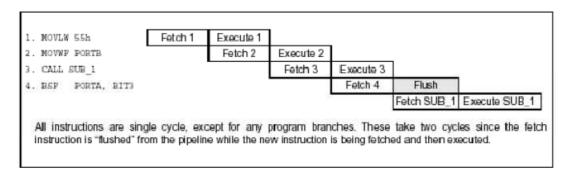

| II.3.5. Exécution d'un programme-notion de pipe-line | 29              |

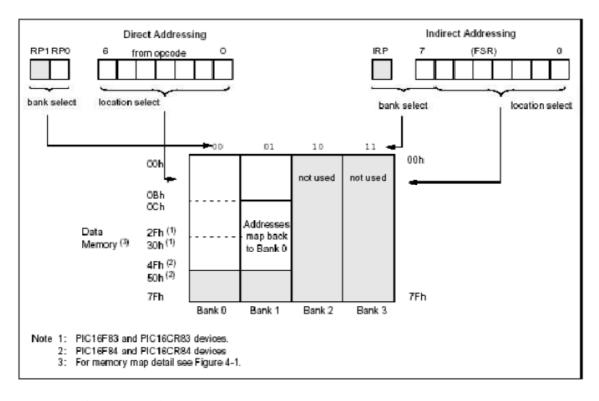

| II.3.6. Modes d'adressages                           | 30              |

| II.3.6.a. Adressage immédiat                         | 31              |

| II.3.6.b. Adressage direct                           | 31              |

| II.3.6.c. Adressage indirect                         | 31              |

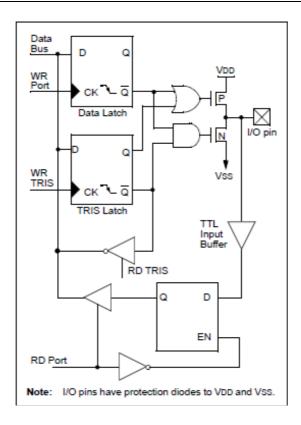

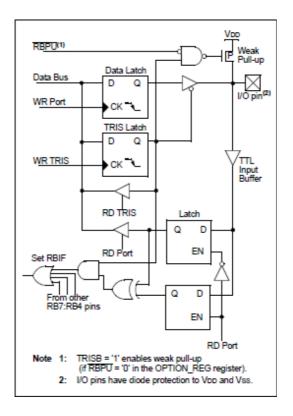

| II.3.7. Ports d'entrées/Sorties                      | 32              |

| II.3.7.a. Port A                                     | 32              |

| <b>II.3.7.b.</b> Port B                                                   | 33    |

|---------------------------------------------------------------------------|-------|

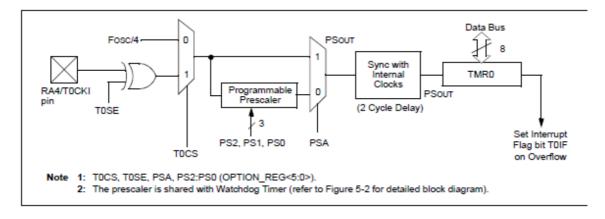

| II.3.8. Compteur                                                          | 34    |

| II.3.8.a. Registre TMR0                                                   | 35    |

| II.3.8.b. Choix de l'horloge                                              | 35    |

| II.3.8.c. Pré-diviseur                                                    | 35    |

| II.3.8.d. Fin de comptage et interruption                                 | 36    |

| II.3.9. Accès à la mémoire EEPORM                                         | 36    |

| II.3.9.a. Lecture                                                         | 37    |

| <b>II.3.9.b.</b> Ecriture                                                 | 37    |

| II.3.10. Interruptions                                                    | 37    |

| II.3.10.a. Différentes sources d'interruption                             | 37    |

| II.3.10.b. Validation des interruptions                                   | 37    |

| II.3.10.c. Séquence de détournement vers le sous-programme d'interruption | on 37 |

| II.3.10.d. Sauvegarde et restitution du contexte                          | 38    |

| II.3.10.e. Retour au programme initial                                    | 38    |

| II.3.11. Chien de garde                                                   | 38    |

| II.3.12. Mode sommeil                                                     | 38    |

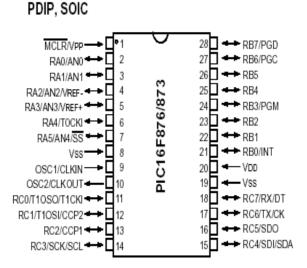

| <i>II.4. PIC 16F876</i>                                                   | 39    |

| II.4.1. Caractéristiques générales                                        | 39    |

| <b>II.4.2.</b> Brochage du 16F876                                         | 40    |

| II.4.3. Les particularités électriques                                    | 40    |

| <b>II.4.4.</b> Organisation du 16F876                                     | 40    |

| II.4.5. Les ports entrée/sortie                                           | 41    |

| II.4.6. L'oscillateur                                                     | 42    |

| II.4.7. MCLR                                                              | 42    |

| II.5. Les différents types de mémoires                                    | 43    |

| II.5.1. RAM                                                               |       |

| II.5.2. ROM                                                               | 43    |

| II.5.2.a. La PROM                                                         | 43    |

| II.5.2.b. L'EPROM                                                         | 43    |

| II.5.2.c. L'EEPROM                                                        | 43    |

| II.5.2.d. La FLASH-EPROM                                                  | 44    |

| II.5.3. Dénomination des mémoires                                         | 44    |

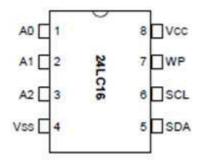

| II.5.4. Description générale de l'EEPROM 24C16                            | 44    |

| II.5.4.a. Brochage de l'EEPROM 24C16                                      | 44    |

| II.5.4.b. Protocole 12C                                                                      | 45              |  |  |

|----------------------------------------------------------------------------------------------|-----------------|--|--|

| Conclusion                                                                                   | 45              |  |  |

| ETUDE EXPERIMENTALE                                                                          |                 |  |  |

| CHAPITRE III : Réalisation du programmateur carte à puce (Gold et<br>Silver) et son lecteur. |                 |  |  |

| PRTIE I : Réalisation de Programmateur.                                                      |                 |  |  |

| III.1.Introduction                                                                           | 46              |  |  |

| III.2.Description du Programmateur carte à puce                                              | 46              |  |  |

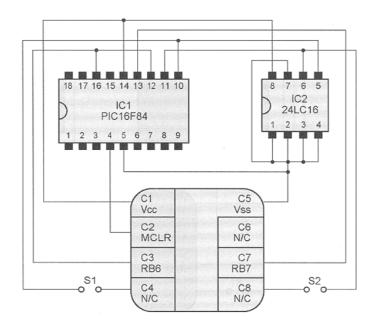

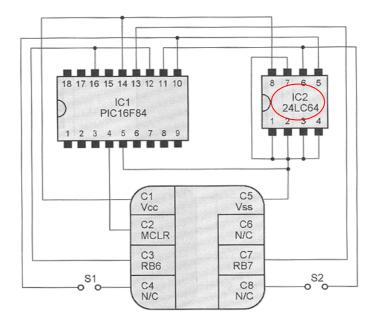

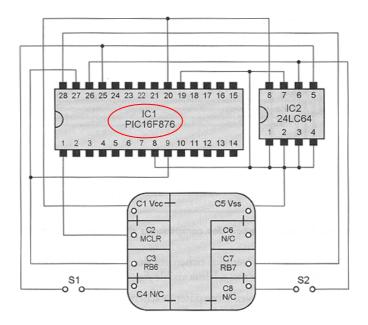

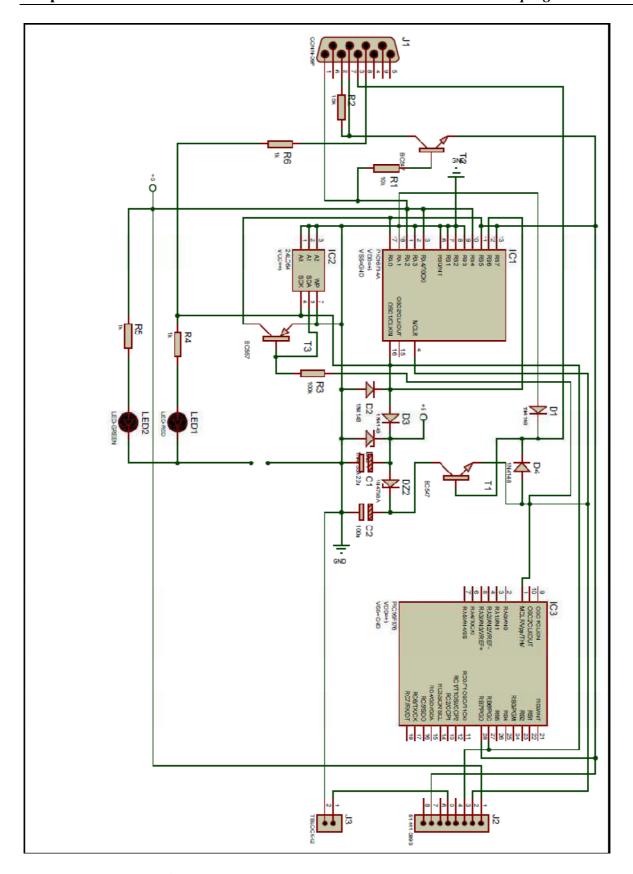

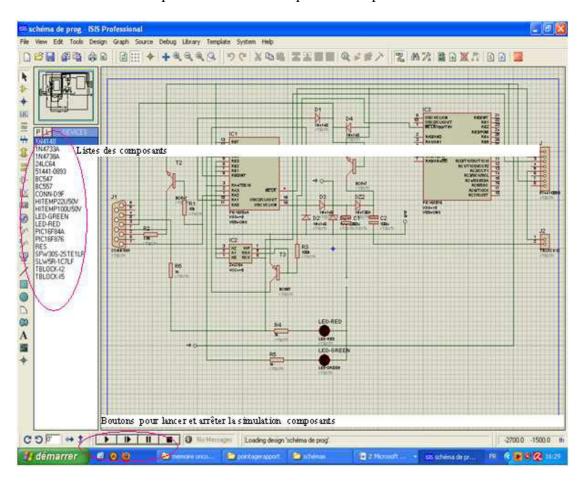

| III.2.1.Schéma du programmateur                                                              | 47              |  |  |

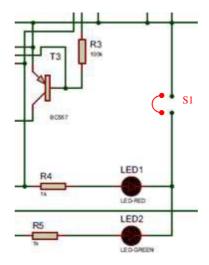

| III.2.2.Principe de fonctionnement                                                           | 49              |  |  |

| III.2.3.Approvisionnement des composants                                                     | 49              |  |  |

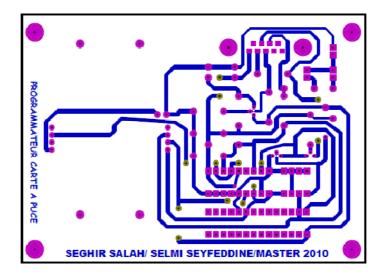

| III.2.4.La réalisation du notre programmateur                                                | 49              |  |  |

| III.2.5. L'implantation des composants                                                       | 50              |  |  |

| III.3.Programmation de notre carte à puce GOLD (pic16f84+24lc16) à V1.0570                   |                 |  |  |

| Conclusion                                                                                   | 55              |  |  |

| PRTIE II : Réalisation de Lecteur.                                                           |                 |  |  |

| III.4.Introduction                                                                           | 56              |  |  |

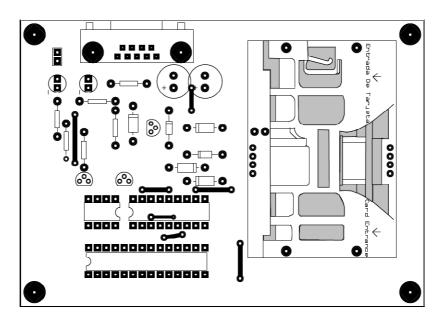

| III.5.Description du lecteur carte à puce (Phoenix ou Smart Mouse)                           | 56              |  |  |

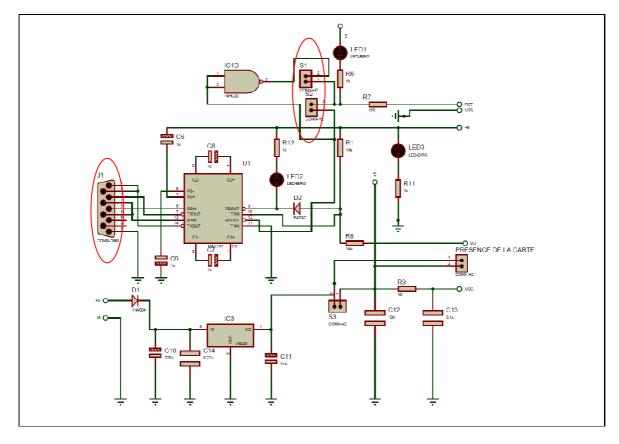

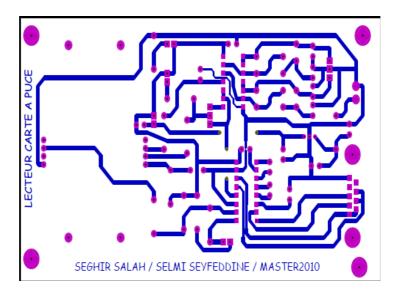

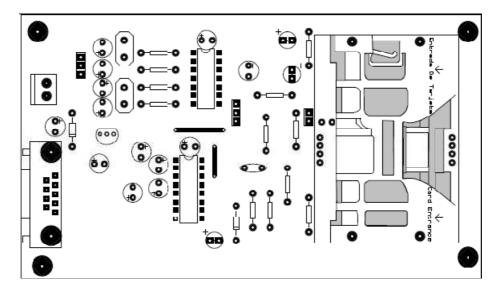

| III.5.1.Schéma du lecteur                                                                    | 56              |  |  |

| III.5.2.Principe de fonctionnement                                                           | 58              |  |  |

| III.5.3.Approvisionnement des composants                                                     | 58              |  |  |

| III.5.4.La réalisation du notre lecteur                                                      | 59              |  |  |

| III.5.5.L'implantation des composants                                                        | 59              |  |  |

| III.6.Lecture de notre carte à puce GOLD (pic16f84+24lc16) à l'aide d                        | IC nua VI 05 61 |  |  |

| 111.6.Lecture de notre carte à pace GOLD (pic10)04+24ic10) à t dide d                        | 1C-progv1.03.01 |  |  |

Conclusion générale et perspectives.

Annexe.

### Liste des figures

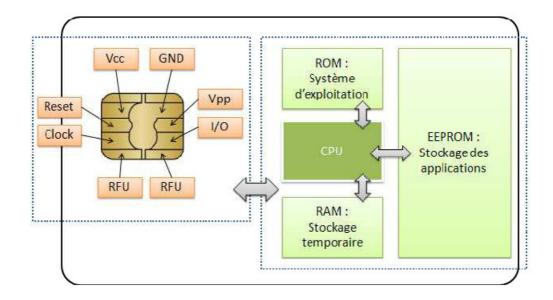

| Figure [I.1]: Architecture de la carte à puce à microcontrôleur                   | 2        |

|-----------------------------------------------------------------------------------|----------|

| Figure [I.2]: positionnement des contacts ISO et AFNOR                            | 3        |

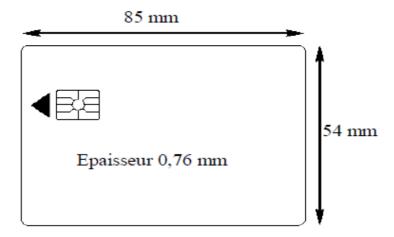

| Figure [I.3] : Dimension de la carte à puce                                       | 4        |

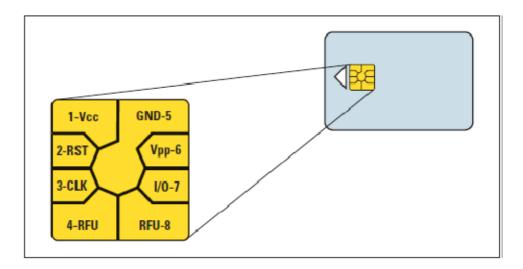

| Figure [I.4]: les contacts de la carte à puce                                     | 5        |

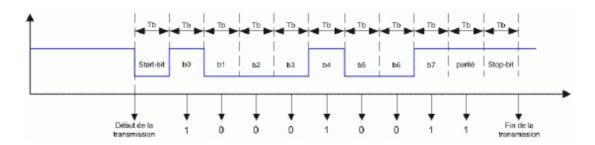

| Figure [I.5] : Chronogramme présentant l'émission d'une donnée par une liaison as | ynchrone |

|                                                                                   | 9        |

| Figure [I.6]: La carte Gold à une couleur dorée                                   | 11       |

| Figure [I.7]: Schéma électronique d'une carte GOLD (Wafer 1)                      | 12.      |

| Figure [I.8]: Schéma électronique d'une carte GOLD 64(Wafer 2)                    | 12       |

| Figure [I.9]: la carte SILVER classique                                           | 13       |

| Figure [I.10] : Schéma électronique d'une carte SILVER                            | 13       |

| Figure [I.11]: Exemple d'un programmateur Carte à Puce PHOENIX en boitier         | 14       |

| Figure [I.12]: Exemple d'un lecteur carte à puce en boitier                       | 14       |

| Figure [I 13]: le modèle de communication de la carte à puce                      | 15       |

| Figure [II.1]: Architecture générale des microcontrôleurs                         | 17       |

| Figure. [II.2]: brochage des PICs 16F8X et 16CR8X                                 | 20       |

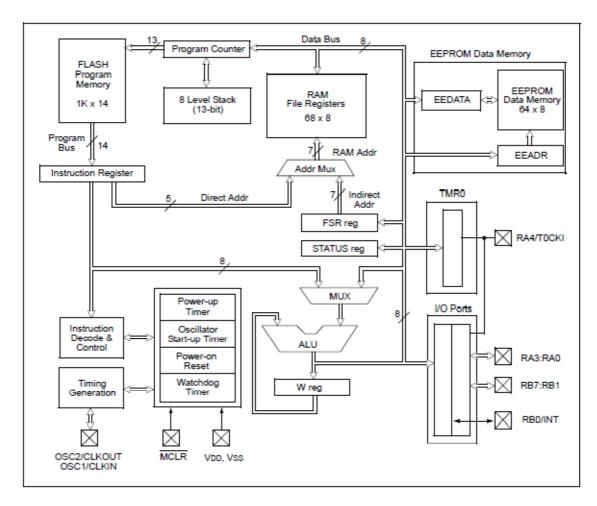

| Figure [II.3]: Architecture générale du PIC 16F84                                 | 21       |

| Figure [II.4] : Organisation de la mémoire de programme et de la pile             | 22       |

| Figure [II.5]: Organisation de la mémoire de données                              | 23       |

| Figure [II.6]: Description des SFR                                                | 24       |

| Figure [II.7]: Format générale des instructions                                   | 26       |

| Figure [II.8]: transfer du registre W dans le registre f                          | 27       |

| Figure [II.9]: Transfer du contenu de registre W dans le registre f               | 29       |

| Figure [II.10]: Transfer d'une constante dans le registre W                       | 28       |

| Figure [II.11]: Liste des instruction du PIC 16F84                                   | 29 |

|--------------------------------------------------------------------------------------|----|

| Figure [II.12]: Enchaînement des instructions                                        | 30 |

| Figure [II.13]: La notion Pipe line du PIC 16F84                                     | 30 |

| Figure [II.14]: Adressage direct et indirect à la mémoire de données                 | 31 |

| Figure [II.15] : Câblage interne d'une patte du part A                               | 33 |

| Figure [II.16] : Câblage interne d'une patte du port B                               | 34 |

| Figure [II.17] : Organigramme du Timer                                               | 34 |

| Figure [II.18]: Valeurs du pré-diviseur en fonction de PSA, PS2, PS1 et PS0          | 36 |

| Figure [II.19]: Brochage du PIC16F876                                                | 40 |

| Figure [II.20]: Brochage de l'EEPROM 24C16                                           | 44 |

| Figure [III.1]: Schéma du notre programmateur                                        | 48 |

| Figure [III.2]: typon (coté cuivre)                                                  | 50 |

| Figure [III.3]: implantations des composants (coté composant)                        | 50 |

| Figure [III.4]: Le programmateur pour cartes Gold et Silver que nous allons réaliser | 51 |

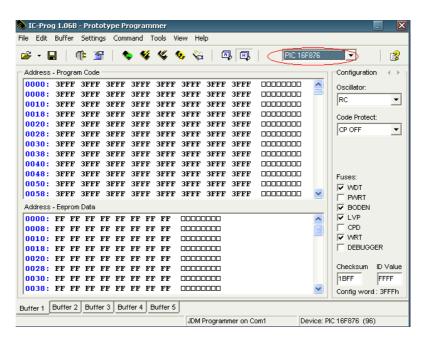

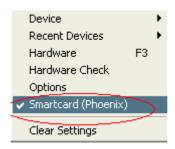

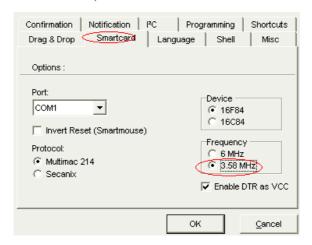

| Figure [III.5]: Configuration du logiciel Ic-Prog                                    | 51 |

| Figure [III.6]: Position du Strap S1                                                 | 52 |

| Figure [III.7]: Sélection du PIC16F84                                                | 52 |

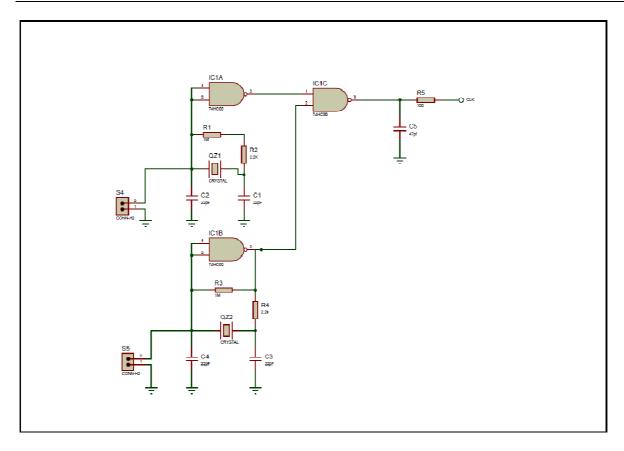

| Figure [III.8] : Schéma de la partie horloge                                         | 57 |

| Figure [III.9] : Schéma électrique du lecteur                                        | 57 |

| Figure [III.10]: typon (coté cuivre)                                                 | 59 |

| Figure [III.11]: implantations des composants (coté composant)                       | 60 |

| Figure [III.12]: Le lecteur Phoenix que nous allons réaliser                         | 60 |

### Résumé

La carte à puce est un nouveau « sésame » dans le monde des électroniciens, elle intervient dans plusieurs applications sensibles tel que les cartes bancaires, carte santé, carte Télévision à péage et le contrôle d'accès sécurisé.

On conclut dans ce mémoire l'étude et la réalisation d'un programmateur de carte à puce et son lecteur.

#### Mot clés:

Carte à puce, Programmateur, Lecteur, Microcontrôleur, Pic.

#### **SUMMARY**

The smart card its new « sesame » in the world of electronics, she entre in a lot of applications sensible such as banks cards ,television cards in toll reod and the secures access control .

It concludes in this memoir the study and realization of the smart card programmer and his reader.

#### **Keywords:**

Smart card, Programmer, Reader, Microcontroller, Pic.

الخلاصة

البطاقة الذكية عبارة عن مفتاح جديد في عالم الالكترونيات ، تدخل في عدة استعمالات حساسة على سبيل الذكر البطاقات البنكية ، البطاقات الصحية ، البطاقات التلفزيونية ذات الدفع المسبق و مراقبة الدخول المؤمن. ونلخص في هذه المذكرة دراسة و انجاز كل من مبرمج البطاقات الذكية و قارئها.

البطاقة الذكية، المبرمج، القارئ، ميكروكنترولر، بيك.

#### INTRODUCTION GENERALE

Pendant la dernière décennie, la carte à puce est en train d'occuper une place de plus en plus importante dans notre société. Même si les gens ne sont pas conscients de cela, chaque fois qu'ils paient leur courses dans des grandes surfaces, achètent leur repas ou retirent de l'argent, ils utilisent une carte à puce.

Cette invention à pointe de la technologie est bien sur présente dans plusieurs domaines, dont le plus connu est celui de la téléphonie mobile – toutes les cartes SIM sont en faite des cartes à puce.

Les cartes à puce fournissent des moyens d'effectuer des applications d'une manière flexible, bloquée, standard, avec l'intervention humaine minimale.

Pour mieux comprendre comment la carte à puce est entrée dans notre quotidien on se doit de rappeler un peu le contexte dans lequel elle est apparue. En 1968, deux Allemands Jürgen Dethloff et Helmut Grötrupp introduisent un circuit intégré dans une carte plastique. Ce n'est juste que quatre ans après que le français Roland Moreno, le père de la carte à puce dépose 47 brevets dans 11 pays. La large étendue de ce brevet nous montre que la carte à puce était considérée comme une invention qui pouvait avoir du succès.

Elle commence à être utilisée pour la première fois en 1983, lors de l'apparition des premières cartes téléphoniques à mémoire. Mais sans-doute le plus grand impact de la carte à puce est survenu lors de l'introduction de la carte bancaire (1987), qui a commencée à être largement utilisée en France d'une manière intensive lors de la dernière décennie.

Nous allons étudier et réaliser un programmateur de carte à puce (Wafer Gold et Silver) et son lecteur. Le but est d'arriver à une conclusion qui à partir d'une étude et réalisation, nous donne un aperçu de programmation (écriture) et lecture de carte à puce.

Pour permettre de bien comprendre l'environnement de programmateur et lecteur des cartes à puces on commencera dans le premier chapitre par l'étude des grandes lignes d'architecture technique de ces dernières.

Dans le deuxième chapitre, nous donnerons les caractéristiques des microcontrôleurs PIC 16F84 et 16F876 qui sont l'essentiel dans notre programmateur.

La deuxième partie : c'est la partie expérimentale.

Dans le premier chapitre on exposera l'étude et la méthode de réalisation de notre programmateur carte à puce (GOLD et SILVER).

Dans le deuxième chapitre, étude et méthode de réalisation de notre lecteur carte à puce.

Enfin la conclusion générale et perspectives pour notre étude et réalisation.

#### Chapitre I

#### Les cartes à puce

#### I.1. Introduction:

La carte à puce est un nouveau « sésame » dans le monde des électroniciens, elle intervient dans plusieurs applications sensibles tel que : les cartes bancaires, carte santé, carte télévision à péage et le contrôle d'accès sécurisé.

#### I.2. Généralités :

#### I.2.1. Définition de la carte à puce :

La carte à puce (Smart Card en anglais), est une carte plastifiée aux dimensions 85,6×54 millimètres avec une épaisseur de l'ordre de 70 à 90 centièmes de millimètres. Elle comporte au moins un circuit intégré (la puce). La carte est un support électronique mobile et fiable pour conserver des secrets. Ces secrets peuvent être des clefs cryptographiques servant à coder ou décoder des messages confidentiels. [1]

#### I.2.2. Classification des cartes à puces :

La classification des cartes à puces est basée sur trois paramètres. [2]

#### I.2.2.a. A base de ces composants :

On distingue deux types de carte :

- a1: La carte à mémoire: c'est une des cartes qui sont les plus communes et les moins chères. Elle contient une EEPROM (Electronic Erasable Programmable Read Only Memory) qui stocke toutes les données de l'application. Sa capacité varie de 2ko à 8ko, et une ROM (Read Only Memory) qui stocke des données qui ne changent jamais pendant la vie de la carte.

- a2: La carte à microcontrôleur: Techniquement, seulement cette carte est digne du nom « carte à puce » qu'on utilise souvent pour tout type de carte. Elle contient une ROM qui contient le système d'exploitation de la carte, une EEPROM qui contient des programmes et des données de l'application de carte, une mémoire versatile RAM (Random Access Memory) qui est utilisée par le processeur pour exécuter des fonctions désireux, un CPU (Central Processing Unit) est le cœur de la carte à puce par exemple : carte GOLD, carte SILVER, carte FUN. La principale différence entre tous ces noms est : le type du microcontrôleur et de l'EEPROM.

Figure [I.1]: Architecture de la carte à puce à microcontrôleur.

#### I.2.2.b. A base de son interface :

On distingue trois types de carte :

b1 : La carte à contact : elle exige de l'introduction dans le lecteur de la carte.

**b2 : La carte sans contact :** elle n'exige pas l'introduction dans le lecteur de la carte.

**b3**: La carte combi ou carte hybride: est ce qui a un contact et une interface sans contact.

#### I.2.2.c. A base de système d'exploitation utilisée :

Le système d'exploitation de la carte à puce généralement appelés SCOS (Smart-card operating system) est embarqué sur la ROM. Il est généralement écrit en language C ou en language assembleur. Il est responsable de :

- Gère les communications avec le monde extérieur.

- Exécute les commandes reçues via I/O.

- Supervise l'exécution des programmes exécutables stockés dans la carte.

- Gère et assure un accès sécurisé à l'ensemble des fichiers.

- Assure les fonctions de cryptographie

Il y a plusieurs systèmes d'exploitation :

✓ <u>Multos</u> : est un système d'exploitation multi-applications pour des cartes qui doivent la sécurité élevé.

✓ JavaCard : des cartes à puces qui exécutent des programmes Java.

#### I.2.3. Positionnement des contacts :

Il y a deux types de positionnement des contacts, la norme ISO (International Organization for Standardization) Internationale et la norme AFNO (Association Française de Normalisation).

Figure [I.2]: positionnement des contacts ISO et AFNOR.

Dans notre travail en utilise les cartes sous norme ISO7816.

#### I.2.4. Norme ISO 7816 : [2]

Le standard ISO7816 contient un ensemble de standards qui couvrent différent aspects des cartes à puce avec contact. Ce standard se décline en plusieurs sous normes que voici :

- > Partie1 : caractéristiques physiques.

- Partie2 : dimensions et position des contacts.

- Partie3 : signaux électroniques et protocoles de transmission.

- Partie4 : commandes inter-industrie pour l'échange.

- > Partie5: identificateur d'application.

- Partie6 : éléments de données inter-industrie.

- ➤ Partie7 : commandes inter-industrie pour SCQL (Structured Card Query Language).

- Partie8 : sécurité de l'architecture et des commandes inter-industrie.

On va détailler une par une ces sous-normes.

#### I.2.4.a. Norme ISO7816-1:

Cette norme définit, comme nous l'avons déjà précisé, les caractéristiques physiques des cartes (Figure I.3) ayant une interface physique par des contacts électrique. Elle ne définit pas la nature, le nombre et la position des circuits intégrés dans la carte. Elle fait référence aux normes

relatives aux cartes d'identification ISO7810, ISO7811 partie 1 à 5, ISO7812 et ISO7813. Les caractéristiques introduites par la norme portent sur :

- La protection contre les ultraviolets et les rayons X.

- Le profil de surface des contacts.

- La résistance mécanique des cartes et des contacts (au pliage, à la torsion).

- La résistance électrique des contacts.

- L'interférence électromagnétique entre les pistes magnétiques éventuelles de la carte et de ses circuits intégrés.

- L'exposition de la carte à des champs magnétiques.

- L'exposition de la carte à une décharge d'électricité statique.

- La dissipation thermique du circuit intégré.

Figure [I.3]: Dimension de la carte à puce.

#### I.2.4.b. Norme ISO7816-2:

La norme ISO7816-2 définit les aspects électriques et la situation des contacts sur la carte. La carte comporte huit contacts (Figure I.4) dont voici l'utilisation :

- Le contact 1 correspond à la tension d'alimentation en lecture(VCC).

- Le contact 2 correspond au signal reset (RST), si une tension appliquée sur ce contact, elle déclenche l'initialisation physique et logique du composant.

- Le contact 3 correspond au signal d'horloge (CLK) il fournit le signal d'horloge externe dont dérivera l'horloge interne.

• Le contact 4 est réservé à une utilisation futur (RFU) « Reserved for Futur Use »

- Le contact 5 correspond à la masse (GND).

- Le contact 6 correspond à la tension d'alimentation (VPP) à appliquer sur demande de la carte, pour programmer la mémoire de données (tension en écriture).il est seulement utilisé sur des cartes anciennes.

- Le contact 7 est le contact d'entrée/sortie (I/O) par lequel transitent en half-duplex toutes les données échangées entre la carte et le monde extérieur.

- Le contact 8 est réservé à une utilisation future(RFU).

Une norme utilisant les contacts RFU serait en cours de préparation pour l'utilisation de l'USB avec la carte.

Figure [I.4]: les contacts de la carte à puce.

#### I.2.4.c. Norme ISO 7816-3:

Cette partie normalise :

- Les caractéristiques électriques comme la fréquence d'horloge (entre 1Mhz et 5Mhz), la vitesse des communications... etc.

- Les protocoles de transmission TPDU (Transmission Protocol Data Unit).

- La sélection de type de protocole PTS (Protocol Type Sélection). Si plusieurs protocoles sont supportés.

- La réponse au reset ATR (Answer To Reset). Qui correspond aux données envoyées par la carte immédiatement après la mise sous tension.

#### I.2.4.d. Norme ISO 7816-4:

ISO 7816-4 vise à assurer une inter-opérabilité. Elle spécifie :

Le contenu des massages entre la carte et le lecteur CAD (Card Acceptance Device).

Qui utilise le protocole APDU (Application Protocole Data Unit) pour les commandes et les réponses.

• Les structures des fichiers et des données : l'accès à ces données, l'architecture de sécurité, la sécurisation des communications.

#### **I.2.4.e. Norme ISO 7816-5:**

Cette norme spécifie le système de numérotation et les procédures d'enregistrement des identifiants d'applications AID (Application Identifier). Les AIDs sont utilisés pour l'identification unique d'une application de la carte et de certains types de fichiers. Un AID est une séquence de 5 à 16 octets. Sa forme est dépendue dans le tableau.

| Application identifier (AID)                   |                                                    |  |

|------------------------------------------------|----------------------------------------------------|--|

| National registered application provider (RID) | Proprietary application identifier extension (PIX) |  |

| 5 octets                                       | 0 à 11 octets                                      |  |

- la première partie RID (Ressource Identifier), de taille fixe, qui fait toujours cinq octets.

- la seconde partie PIX (Proprietary Identifier eXtension), de taille variant entre 0 et 11 octets.

#### I.2.4.f. Norme ISO 7816-6:

Cette norme spécifie les éléments de données inter-industrie pour les échanges, tels que le numéro du porteur de carte, sa photo, sa langue, la date d'expiration,....etc.

#### **I.2.4.g.** Norme ISO 7816-7:

Cette norme propose des commandes inter-industrie pour SCQL. Elle est destinée à la gestion de base de données à l'intérieur de la carte. Son utilisation actuellement serait très marginale.

#### I.2.4.h. Norme ISO 7816-8:

La norme concerne la sécurité de l'architecture et des commandes inter-industrie. Les informations sur cette partie ne nous sont pas accessibles pour le moment.

#### I.2.5. Spécification de la norme ISO 7816 :

- La carte ne dispose pas de sa propre horloge, elle est fournie par l'interface, ou maître (Dans notre cas c'est le PIC16F84 (gold) et le PIC16F876 (silver)), et est généralement sous la barre des 4MHZ.

- Le temps séparant chaque bit est définit par la norme comme étant de 1bit émis toutes les 372 impulsions de l'horloge du maître .Ceci donne un débit de l'ordre de 9600 bits/s avec un Quartz de 3.579 MHZ.

- La communication est du type half-duplex, c'est-à-dire que les entrées et les sorties s'effectuent par alternance et en se servant de la même ligne physique.

- La transmission est du type asynchrone, avec 1 bit de START ,8 bits de données,1 bit de parité pair, et 2 bits de stop.

#### I.2.6. Les commandes ISO 7816:

La carte ne prend jamais l'initiative de l'échange d'information .Elle ne fait que répondre à des commandes de la forme :

| CLASSE | INSTRUCTION | PARAMETRE1 | PARAMETRE2 | LONGUEUR |

|--------|-------------|------------|------------|----------|

|        |             |            |            |          |

Ou encore sous forme abrégée :

CLASS INS P1 P2 LEN

Les significations de chacun des ses octets de la commande reçu se présente comme suit :

- **CLASS** : détermine le groupe d'instructions concernées.

- **INS**: c'est l'instruction proprement dite, ou encore la commande. C'est elle qui détermine l'opération à effectuer par la carte.

- P1 et P2 : sont deux paramètres que la carte reçoit avec la commande. Leur signification dépend de la commande envoyée. Ils peuvent être inutilisés mais doivent tout de même être présents.

• LEN: peut représenter deux choses: soit c'est le nombre d'octet qui suit la commande, dans ce cas la carte s'attendra à recevoir LEN octets supplémentaires, avant de traiter la commande dans sa totalité. Soit ce sera la longueur de la chaîne de réponse que le maître s'attend à recevoir en provenance de la carte. C'est INS qui permet d'établir le rôle de LEN.

#### I.2.7. Le protocole d'échange d'informations :

L'échange standard d'informations entre le maître et la carte selon la norme ISO 7816, se déroule comme suit :

- A la mise en service, le maître génère un RESET sur la pine MCLR, la carte répond avec un certain nombre d'octets. Cette réponse s'appelle : ATR, pour « Answer To RESET ».

- Le maître envoie la commande sous la forme : Class INS P1 P2 LEN

- La carte renvoie l'instruction comme accusée de réception **INS**.

- Le maître envoie éventuellement les données complémentaires.

- La carte envoie la réponse.

- La carte envoie le statut et repasse en mode d'attente de commande.

#### I.2.8. Les liaisons asynchrones : [4]

Asynchrone, il s'agit donc d'une liaison qui ne fournit pas une horloge destinée à indiquer le début et la fin de chaque bit envoyé. Nous aurons donc besoin d'un mécanisme destiné à repérer la position de chaque bit. Il s'agit d'un mode asynchrone particulier où un bit est donné toutes les 372 impulsions d'horloge.

Pour recevoir correctement les bits envoyés, il faut convenir d'un protocole de communication. Ce dernier doit fixer les informations suivantes :

- La vitesse de transmission en bauds (bits par seconde).

- Le format, c'est-à-dire le nombre de bit de START, de bit de stop, de bits de données et le type de parité.

Nous allons maintenant expliquer ces concepts et indiquer quelles sont les valeurs employées dans la norme ISO 7816.

■ Le bit de START\_: Au repos, la ligne se trouve à l'état haut. L'émetteur fait alors passer la ligne à l'état bas : c'est-à-dire le bit de START. C'est ce changement de niveau qui va permettre de détecter le début de la réception des bits en série. Les valeurs admissibles sont 1 ou 2 bits START (x). La norme ISO 7816 utilise un seul bit de START à zéro « 0 ».

■ Les bits de donnée: Après avoir reçu le bit START, on trouve les bits de données. Les normes usuelles utilisent 7 ou 8 bits de données. Pour la norme ISO 7816, il y a 8 bits de données, ce qui autorise des valeurs admissibles de 0 à 0xFF pour chaque octet reçu.

- Le bit de parité : Le bit de parité est une vérification du bon déroulement du transfert. Dans la norme ISO7816 on utilise une parité paire.

- Le bit stop (stop-bit): Après la réception des bits précédents, il est impératif de remettre la ligne à l'état haut pour pouvoir détecter le bit START de l'octet suivant. C'est le rôle du STOP-Bit. Les valeurs admissibles sont de 1 ou 2 STOP-Bits.

Voici, pour illustrer tout ceci, l'émission d'une donnée codée sur 8 bits, avec parité paire et un STOP-Bit. Les lectures sont indiquées par les flèches inférieures :

**Figure [I.5] :** Chronogramme présentant l'émission d'une donnée par une liaison asynchrone.

■ Vitesse et débit : La durée de transmission d'un bit est constante et dépend de la vitesse 9600 bits/secondes, c'est-à-dire, chaque bit durera 1s/9600=104.17µS.

Dans le cas de la norme ISO 7816, nous utiliserons 1 bit START+8bits de données +1 bit de parité+2 bits de stop=12bits. Le temps total pour recevoir une trame est donc de 1250µs.

#### I.2.9. Avantages de la carte à puce:

Les avantages de la carte à puce sont la sécurité, la portabilité, la facilité d'utilisation et la personnalisation. La carte à puce est résistante aux attaques car elle n'a pas besoin d'être dépendante d'une ressource externe potentiellement vulnérable. La sécurité de la carte à puce se fait à plusieurs niveaux :

#### I.2.9.a. Au niveau physique:

• Par des techniques d'impression sur le corps de carte très sophistiquées.

#### I.2.9.b. Au niveau Hardware:

• Par un numéro de série unique.

- Par l'utilisation de mémoire de type PROM (Programmable Read Only Memory).

L'information peut être stockée de manière durable hors-usine et aussi être déplacée par moment à l'intérieur de cette mémoire afin d'éviter des attaques localisées.

- Par blindage physique du composant par collage du micro chip au micromodule avec des techniques spécialisées et insertion des couches métallisé.

- Par contrôle des accès aux mémoires (EEPROM, ROM).

#### I.2.9.c. Au niveau software:

- Par des contrôles d'accès aux données grâce, par exemple, à un code secrets ou par authentification cryptographique.

- Par un maintien de l'intégrité des données en utilisant la vérification des témoins, les calcules de signatures sur les données internes.

- Grace à des entrées/sortie sécurisées par chiffrement/signature et temps d'exécution des commandes constants.

#### I.2.10. Applications des cartes à puces :

Les principaux secteurs qui utilisent la carte à puce sont :

- ✓ L'industrie des télécommunications par exemple les cartes téléphoniques prépayées, les carte SIMs insérées dans les téléphones GSM, ... etc.

- ✓ L'industrie bancaire et monétaire avec les cartes de crédits qui sont des cartes à microprocesseur avec contact.

- ✓ Le secteur de la santé.

- ✓ Le contrôle d'accès physique des personnes à des locaux.

- ✓ Le porte-monnaie électronique.

- ✓ L'industrie audiovisuelle avec la télévision à péage, ... etc.

Pour notre application, on a choisi les cartes de type GOLD et SILVER, possédant un microcontrôleur PIC de type 16F84(GOLD) et 16F876(SILVER) et une mémoire 24C16

(GOLD) et 24C64 (SILVER). Ce type de cartes permet de garantir des performances au niveau puissance de microcontrôleur et grande capacité de mémoire intégrée.

#### **I.3.** La carte GOLD: [10]

Même si elle est encore disponible sur le marché car elle peut recevoir de nombreux applications, cette carte est historiquement la première à avoir été réalisée si l'on excepte les Basic Card qui constituent une famille à part. Elle est de ce fait plus simple que certaines cartes actuelles, compte tenu de son âge et donc des composants qui étaient disponibles à l'époque de sa conception. Comme le montre son schéma ci-dessous, elle ne contient en effet qu'un classique microcontrôleur PIC 16F84 associé à une mémoire EEPROM série externe de type 24LC16 (figure I.7). Cette approche, qui a de quoi surprendre puisque le 16F84 contient déjà en interne une mémoire EEPROM de données, est justifiée par le fait que la taille de cette mémoire est très réduite puisqu'elle n'est que de 64 octets. L'ajout de la 24LC16 externe permet de porter cette capacité de mémorisation à 2 K octets ce qui est déjà plus confortable. Cette carte est appelée à la quasi-unanimité carte Wafer 1 ou bien encore carte Gold en raison de la couleur dorée de certaines versions.

Figure [I.6]: La carte Gold a une couleur dorée. [S1]

Figure [I.7]: Schéma électronique d'une carte GOLD (Wafer 1). [S1]

La carte Gold existe aussi sous la dénomination Wafer 2 ou bien encore Gold 64. Son schéma est alors identique à celui de la Wafer 1, comme le montre la figure I.8, mais la mémoire EEPROM devient de la 24LC64 c'est à dire qu'elle offre une capacité de 8 K octets.

Figure [I.8]: Schéma électronique d'une carte GOLD 64(Wafer 2). [S1]

#### I.4. La carte SILVER: [10]

Appelée carte Wafer3 ou carte SILVER, car de nombreuses versions de cette carte sont disponibles sous une belle livrée argentée, cette carte reste fidèle à la famille PIC de Microchip, mais fait appel à un circuit plus richement doté en ressources internes avec le 16F876, comme le montre son schéma visible ci-dessous.

Figure [I.9]: la carte SILVER classique. [S2]

Figure [I.10]: Schéma électronique d'une carte SILVER. [S2]

Pour travailler avec une carte à puce, il faut avoir au moins deux appareils :

- ♣ Appareil d'écriture (qui est le programmateur de carte à puce).

- ♣ Appareil de lecture.

#### I.5. Programmateur de carte à puce : [9]

Programmateur de carte à puce est un dérivé de JDM Programmer (programmateur des pic) équipé des ports USB ou ports série. Il permet de la programmation extrêmement rapide de toutes les cartes à puces à base de microcontrôleurs PIC et ATMEL, (Gold, Silver, Fun, ATmega, ...etc.) à l'aide de son logiciel. Le port série permet d'utiliser les logiciels compatibles avec le mode Phoenix ou Smart Mouse en 3,58MHz, 3,68MHz ou 6,00MHz pour la programmation des cartes sécurisées.

Figure [I.11]: Exemple d'un programmateur Carte à Puce PHOENIX en boitier.

#### I.6. Lecteur carte à puce : [6]

Le lecteur est le point de passage obligé pour lire dans n'importe quelle carte à puce et aussi est un terminal intelligent qui prend plus ou moins largement en charge les protocoles de communication avec les cartes à puce.

Tout lecteur de carte à puce, associé à son logiciel « ou driver », se charge de toutes les protocoles de communication normalisés.

Figure [I.12]: Exemple d'un lecteur carte à puce.

#### I.7. La communication entre le lecteur et la carte à puce : [6]

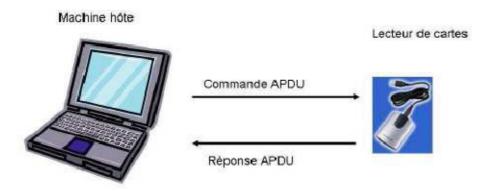

Echange de commandes avec le lecteur de carte à puce tel que défini dans l'ISO 7816-4. La communication entre l'hôte et la carte est half-duplex. Elle se fait à l'aide de paquets appelés APDU (Application Protocol Data Units) en respectant le protocole de l'ISO 7816-4. Un APDU contient une commande ou une réponse. Le mode Maître/Esclave est utilisé. Ainsi la carte joue un rôle passif et attend une commande APDU à partir de l'hôte. Elle exécute l'instruction spécifiée dans la commande et retourne une réponse APDU.

Figure [I.13]: le modèle de communication de la carte à puce.

#### **Conclusion:**

La carte à puce est un outil très puissant. On peut le considérer comme un petit ordinateur. L'avantage le plus important de la carte à puce est sa sécurité, d'autre part avec la taille petite, cet outil rend la commodité dans l'utilisation.

Pour construire une application de la carte à puce. On doit développer parallèlement trois parties qui sont le langage de programmation, le programmateur de carte à puce et le lecteur de carte à puce.

Le choix d'un lecteur ou d'un programmateur de carte dépend de ce que nous voulant faire, mais aussi et surtout des types de cartes que nous voulant lire ou programmer.

#### **Chapitre II**

#### Les microcontrôleurs (PIC) et mémoires

#### **II.1 Introduction:**

Un microcontrôleur est un composant électronique autonome. Il est généralement moins puissant qu'un microprocesseur en terme de rapidité ou de taille mémoire, il se contente le plus souvent d'un bus de 8 ou de 16 bits. Ce que fait que c'est un composant très bon marché parfaitement adapte pour piloter les applications embarquées dans de nombreux domaines d'application. Nous pensons qu'on ne se tromperait pas beaucoup si on affirme qu'aujourd'hui il y'a un microcontrôleur (± grand) dans chaque équipement électronique :

- Informatique (souris, modem, ...etc.);

- Vidéo (Appareil photos numérique, caméra numérique, ...etc.);

- Contrôle des processus industriels (régulation, pilotage) ;

- Appareil de mesure (affichage, calcul statistique, mémorisation);

- Automobile (ABS, injection, GPS, airbag);

- Multimédia (téléviseur, carte audio, carte vidéo, magnétoscope);

- Téléphones (fax, portable, modem);

- Carte à puce (GOLD, SILVER, FUN...etc.).

Plusieurs constructeurs se partagent le marché des microcontrôleurs, citons INTEL, MOTOROLA, ATMEL, ZILOG, PHILIPS et enfin MICROCHIP avec ses PICs très populaires qui nous intéresse ici dans ce projet.

On peut dire que seul le langage de programmation (Assembleurs) constitue la différence majeure en deux microcontrôleurs (similaires) venant de deux constructeurs différents.

Nous avons choisit dans ce chapitre d'apprendre les microcontrôleurs à travers une étude détaillée des microcontrôleurs 16F84 et 16F876, qui sont constitue les éléments fondamentaux de la famille mid-Line qui est la famille « moyenne puissance » de MICROCHIP.

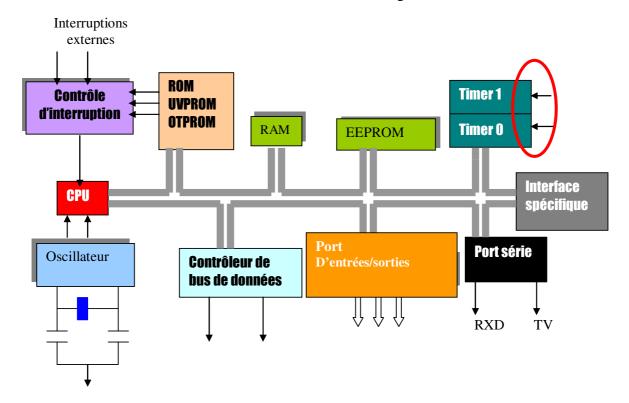

#### II.2 Généralités:

Les microcontrôleurs, quelque soit leurs constructeurs, ont des architectures très similaires et sont constitués des modules fondamentaux assurant les mêmes fonctions:

- UAL (Unité Arithmétique et Logique).

- Ports d'E/S

- interfaces de communications série

- Interfaces d'E/S analogiques

- Timers et horloge temps réels.

En illustrons l'architecture des microcontrôleurs dans la figure suivante.

Figure [II.1]: Architecture générale des microcontrôleurs.

Un PIC est un microcontrôleur de chez Microchip. Ses caractéristiques principales sont:

- ➤ Séparation des mémoires de programme et de données (architecture Hardware) : on obtient ainsi une meilleure bande passante et des instructions et des données pas forcément codées sur le même nombre de bits.

- Communication avec l'extérieur seulement par des ports : il ne possède pas de bus d'adresses, de bus de données et de bus de contrôle comme la plupart des microprocesseurs.

➤ Utilisation d'un jeu d'instruction réduit, d'où le nom de son architecture : RISC (Reduced Instructions Set Construction). Les instructions sont ainsi codées sur un nombre réduit de bits, ce qui accélère l'exécution (1 cycle machine par instruction sauf pour les sauts qui requirent 2 cycles). En revanche, leur nombre limité oblige à se restreindre à des instructions basiques, contrairement aux systèmes d'architecture CISC (Complex Instructions Set Construction) qui proposent plus d'instructions donc codées sur plus de bits, mais réalisant des traitements plus complexes.

#### Il existe trois familles de PIC:

- Base-Line: Les instructions sont codées sur 12 bits.

- Mid-Line: Les instructions sont codées sur 14 bits.

- High-End: Les instructions sont codées sur 16 bits.

Un PIC est identifié par un numéro de la forme suivante :

$$xx(L) XXyy-zz$$

- **xx**: Famille du composant (12, 14, 16, 17, 18)

- L: Tolérance plus importante de la plage de tension

- **XX**: Type de mémoire de programme :

- ✓  $C \rightarrow \text{EPROM ou EEPROM}$

- $\checkmark$   $CR \rightarrow PROM$

- $\checkmark$   $F \rightarrow FLASH$

- yy: Identification

- **zz**: Vitesse maximum du quartz

#### Par exemple PIC 16F84 –10, soit :

- 16 : Mid-Line

- F: FLASH

- 84 : Type

- 10 : Quartz à 10MHz au maximum

#### II.3. Le PIC 16F84: [7]

Ce modèle de PIC (*Programmable Interface Contrôler*) est un circuit de petite taille, fabriqué par la Société américaine *Arizona MICROCHIP Technologie*.

En le regardant pour la première fois, il fait davantage penser à un banal circuit intégré logique TTL ou MOS, plutôt qu'à un microcontrôleur.

Son boîtier est un DIL (*Dual In Line*) de 2x9 pattes.

En dépit de sa petite taille, il est caractérisé par une architecture interne qui lui confère souplesse et vitesse incomparables.

Ses principales caractéristiques sont :

- 13 lignes d'entrées/sorties, réparties en un port de 5 lignes (Port A) et un port de 8 lignes (Port B)

- alimentation sous 5 Volts

- architecture interne révolutionnaire lui conférant une extraordinaire rapidité

- une mémoire de programme pouvant contenir 1.019 instructions de 14 bits chacune (allant de l'adresse 005 à l'adresse 3FF)

- une mémoire RAM utilisateur de 68 emplacements à 8 bits (de l'adresse 0C à l'adresse 4F)

- une mémoire RAM de 2x12 emplacements réservée aux registres spéciaux

- une mémoire EEPROM de 64 emplacements

- une horloge interne, avec pré diviseur et chien de garde

- possibilité d'être programmé en mode *in-circuit*, c'est à dire sans qu'il soit nécessaire de le retirer du support de l'application

- vecteur de Reset situé à l'adresse 000

- un vecteur d'interruption, situé à l'adresse 004

- bus d'adresses de 13 lignes

- présence d'un code de protection permettant d'en empêcher la duplication

- facilité de programmation, simplicité et faible prix.

- 35 instructions codées sur 14 bits.

- Données sur 8 bits.

- 1 cycle machine par instruction, sauf pour les sauts (2 cycles machines).

- Vitesse maximum 10 MHz soit une instruction en 400 ns (1 cycle machine = cycles d'horloge).

- 4 sources d'interruption.

- 1000 cycles d'effacement/écriture pour la mémoire flash, 10.000.000 pour la mémoire de donnée EEPROM

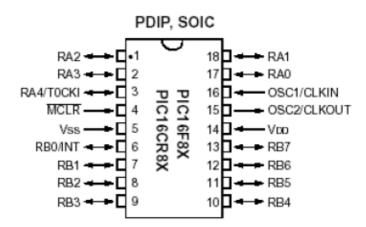

#### II.3.1. Brochage du 16F84 : [12]

La figure [II.2] montre le brochage de circuit intégré des pics 16F8X. Les fonctions des pattes sont les suivantes :

✓ VSS, VDD : Alimentation

✓ **OSC1, 2** : Horloge

✓ **RA0-4**: Port A

✓ **RB0-7**: Port B

✓ **T0CKL** : Entrée de comptage

✓ **INT**: Entrée d'interruption

$\checkmark$  MCLR: Reset: 0V

Choix du mode : - programmation : 12V - 14V

- exécution : 4.5V - 5.5V

Figure. [II.2]: brochage des PICs 16F8X et 16CR8X.

#### II.3.2. Architecture générale : [12]

La Figure [II.3] présente l'architecture générale d'un PIC. Il est constitué des éléments suivants :

Figure [II.3]: Architecture générale du PIC 16F84.

- ✓ un système d'initialisation à la mise sous tension (Power-up Timer, Oscillator Stratup Timer,...etc.).

- ✓ un système de génération d'horloge à partir du quartz externe (Timing Generation).

- ✓ une unité arithmétique et logique (UAL ou en anglais ALU).

- ✓ une mémoire flash pour programme de 1k "mots" de 14 bits.

- ✓ un compteur de programme (Program Counter) et une pile (Stack).

- ✓ un bus spécifique pour le programme (Program Bus).

- ✓ un registre contenant le code de l'instruction à exécuter (Instruction Register).

- ✓ un bus spécifique pour les données (Data Bus).

- ✓ une mémoire RAM de 68 emplacements à 8 bits.

- ✓ les SFR(Special Function Registers).

- ✓ une mémoire EEPROM de 64 octets de données.

- ✓ deux ports d'entrées/sorties.

- ✓ un compteur (Timer).

- ✓ un chien de garde (Watchdog).

#### II.3.3. Organisation de la mémoire : [7]

Le PIC contient une mémoire pour le programme et une mémoire pour les données. La structure Hardware des PICs fournit un accès séparé à chacune. Ainsi, un accès aux deux est possible pendant le même cycle machine.

#### II.3.3.a. Mémoire de programme :

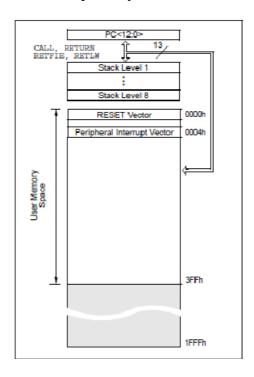

C'est elle qui contient le programme à exécuter. Ce dernier est chargé par liaison série. La Figure [II.4] montre l'organisation interne de cette mémoire. Elle contient 1k "mots" de 14 bits dans le cas du PIC 16F84, même si le compteur de programme (PC) de 13 bits peut en adresser 8k. Il faut se méfier des adresses images! L'adresse 0000h contient le vecteur du reset, l'adresse 0004h l'unique vecteur d'interruption du PIC. La pile contient 8 valeurs. Comme le compteur de programme, elle n'a pas d'adresse dans la plage de mémoire. Ce sont des zones réservées par le système.

Figure [II.4]: Organisation de la mémoire de programme et de la pile.

## II.3.3.b. Mémoire de données :

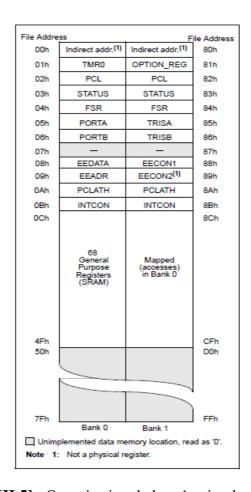

Elle se décompose en deux parties de RAM (Figure [II.5]) et une zone EEPROM. La première contient les SFRs (Special Function Registers) qui permettent de contrôler les opérations sur le circuit. La seconde contient des registres généraux, libres pour l'utilisateur. La dernière contient 64 octets.

Figure [II.5] : Organisation de la mémoire de données.

Les instructions orientées octets ou bits contiennent une adresse sur 7 bits pour désigner l'octet avec lequel l'instruction doit travailler. D'après la Figure [II.5], l'accès au registre TRISA d'adresse 85h, par exemple, est impossible avec une adresse sur 7 bits. C'est pourquoi le constructeur a défini deux banques. Le bit Rb0 du registre d'état (STATUS.5) permet de choisir entre les deux. Ainsi, une adresse sur 8 bits est composée de RP0 en poids fort et des 7 bits provenant de l'instruction à exécuter.

## b1 : Registres généraux :

Ils sont accessibles soit directement, soit indirectement à travers les registres FSR et INDF.

## b2: Registres spéciaux - SFRs:

Ils permettent la gestion du circuit. Certains ont une fonction générale, d'autres une fonction spécifique attachée à un périphérique donné. La Figure [II.6] donne la fonction de chacun des bits de ces registres. Ils sont situés de l'adresse 00h à l'adresse 0Bh dans la banque 0 et de l'adresse 8Bh à l'adresse 8Bh dans la banque 1. Les registres 07h et 87h n'existent pas.

| Addr                                                                           | Name                  | Bit 7                                                                 | Bit 6                                                  | Bit 5      | Bit 4                         | Bit 3 | Bit 2 | Bit 1  | Bit 0     | Value on<br>Power-on<br>RESET | Details<br>on page |

|--------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|--------------------------------------------------------|------------|-------------------------------|-------|-------|--------|-----------|-------------------------------|--------------------|

| Bank 0                                                                         |                       |                                                                       |                                                        |            |                               |       |       |        |           |                               |                    |

| 00h INDF Uses contents of FSR to address Data Memory (not a physical register) |                       |                                                                       |                                                        |            |                               |       |       |        |           | 11                            |                    |

| 01h                                                                            | TMR0                  | 8-bit Rea                                                             | 8-bit Real-Time Clock/Counter                          |            |                               |       |       |        |           |                               | 20                 |

| 02h                                                                            | PCL                   | Low Ord                                                               | er 8 bits of t                                         | ne Prograi | m Counter (P                  | C)    |       |        |           | 0000 0000                     | 11                 |

| 03h                                                                            | STATUS <sup>(2)</sup> | IRP                                                                   | RP1                                                    | RP0        | TO                            | PD    | Z     | DC     | c         | 0001 1xxx                     | 8                  |

| 04h                                                                            | FSR                   | Indirect Data Memory Address Pointer 0                                |                                                        |            |                               |       |       |        |           | XXXX XXXX                     | 11                 |

| 05h                                                                            | PORTA <sup>(4)</sup>  | _                                                                     | _                                                      | _          | RA4/T0CKI                     | RA3   | RA2   | RA1    | RA0       | x xxxx                        | 16                 |

| 06h                                                                            | PORTB <sup>(5)</sup>  | RB7                                                                   | RB6                                                    | RB5        | RB4                           | RB3   | RB2   | RB1    | RB0/INT   | XXXX XXXX                     | 18                 |

| 07h                                                                            | _                     | Unimpler                                                              | Unimplemented location, read as '0'                    |            |                               |       |       |        |           |                               | _                  |

| 08h                                                                            | EEDATA                | EEPROM Data Register                                                  |                                                        |            |                               |       |       |        | XXXX XXXX | 13,14                         |                    |

| 09h                                                                            | EEADR                 | EEPROM Address Register                                               |                                                        |            |                               |       |       |        | XXXX XXXX | 13,14                         |                    |

| 0Ah                                                                            | PCLATH                | _                                                                     | Write Buffer for upper 5 bits of the PC <sup>(1)</sup> |            |                               |       |       |        | 0 0000    | 11                            |                    |

| 0Bh                                                                            | INTCON                | GIE                                                                   | EEIE                                                   | TOIE       | TOIE INTE RBIE TOIF INTF RBIF |       |       |        |           |                               | 10                 |

| Bank                                                                           | 1                     |                                                                       |                                                        |            | •                             |       |       |        |           | •                             |                    |

| 80h                                                                            | INDF                  | Uses Contents of FSR to address Data Memory (not a physical register) |                                                        |            |                               |       |       |        |           |                               | 11                 |

| 81h                                                                            | OPTION_REG            | RBPU                                                                  | INTEDG                                                 | TOCS       | TOSE                          | PSA   | PS2   | PS1    | PS0       | 1111 1111                     | 9                  |

| 82h                                                                            | PCL                   | Low order 8 bits of Program Counter (PC)                              |                                                        |            |                               |       |       |        |           | 0000 0000                     | 11                 |

| 83h                                                                            | STATUS (2)            | IRP                                                                   | RP1                                                    | RP0        | TO                            | PD    | Z     | DC     | С         | 0001 1xxx                     | 8                  |

| 84h                                                                            | FSR                   | Indirect data memory address pointer 0                                |                                                        |            |                               |       |       |        |           | XXXX XXXX                     | 11                 |

| 85h                                                                            | TRISA                 | PORTA Data Direction Register                                         |                                                        |            |                               |       |       |        | 1 1111    | 16                            |                    |

| 86h                                                                            | TRISB                 | PORTB Data Direction Register                                         |                                                        |            |                               |       |       |        | 1111 1111 | 18                            |                    |

| 87h                                                                            | _                     | Unimplemented location, read as '0'                                   |                                                        |            |                               |       |       |        | _         | _                             |                    |

| 88h                                                                            | EECON1                | _                                                                     | _                                                      | _          | EEIF                          | WRERR | WREN  | WR     | RD        | 0 x000                        | 13                 |

| 89h                                                                            | EECON2                | EEPROM Control Register 2 (not a physical register)                   |                                                        |            |                               |       |       |        |           | 14                            |                    |

| 0Ah                                                                            | PCLATH                | Write buffer for upper 5 bits of the PC <sup>(1)</sup>                |                                                        |            |                               |       |       | 0 0000 | 11        |                               |                    |

| 0Bh                                                                            | INTCON                | GIE                                                                   | EEIE                                                   | TOIE       | INTE                          | RBIE  | TOIF  | INTF   | RBIF      | 0000 000x                     | 10                 |

Legend: x = unknown, u = unchanged. - = unimplemented, read as '0', q = value depends on condition

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> are never transferred to PCLATH.

- 2: The TO and PD status bits in the STATUS register are not affected by a MCLR Reset.

- 3: Other (non power-up) RESETS include: external RESET through MCLR and the Watchdog Timer Reset.

- 4: On any device RESET, these pins are configured as inputs.

- 5: This is the value that will be in the port output latch.

**Figure [II.6] :** Description des SFR.

On donne la description des registres spéciaux :

- INDF (00h-80h) : Utilise le contenu de FSR pour l'accès indirect à la mémoire.

- TMR0 (01h) : Registre lié au compteur.

- PCL (02h-82h): Contient les poids faibles du compteur de programmes (PC). Le registre PCLATH (0Ah-8Ah) contient les poids forts.

- STATUS (03h-83h): Il contient l'état de l'unité arithmétique et logique ainsi que les bits de sélection des banques.

- FSR (04h-84h) : Permet l'adressage indirect

- PORTA (05h): Donne accès en lecture ou écriture au port A, 5 bits. Les sorties sont à drain ouvert. Le bit 4 peut être utilisé en entrée de comptage.

- PORTB (06h) : Donne accès en lecture ou écriture au port B. Les sorties sont à drain ouvert. Le bit 0 peut être utilisé en entrée d'interruption.

- EEDATA (08h): Permet l'accès aux données dans la mémoire EEPROM.

- EEADR (09h): Permet l'accès aux adresses de la mémoire EEPROM.

- PCLATCH (0Ah-8Ah) : Donne accès en écriture aux bits de poids forts du compteur de programme.

- INTCON (0Bh-8Bh) : Masque d'interruptions.

- OPTION\_REG (81h) : Contient des bits de configuration pour divers périphériques.

- TRISA (85h) : Indique la direction (entrée ou sortie) du port A.

- TRISB (86h) : Indique la direction (entrée ou sortie) du port B.

- EECON1 (88h): Permet le contrôle d'accès à la mémoire EEPROM.

- EECON2 (89h) : Permet le contrôle d'accès à la mémoire EEPROM.

#### **b3. Mémoire EEPROM:**

Le PIC possède une zone EEPROM de 64 octets accessibles en lecture et en écriture par le programme. On peut y sauvegarder des valeurs, qui seront conservées même si l'alimentation est éteinte, et les récupérer lors de la mise sous tension. Leur accès est spécifique et requiert l'utilisation de registres dédiés. La lecture et l'écriture ne peut s'exécuter que selon des séquences particulières.

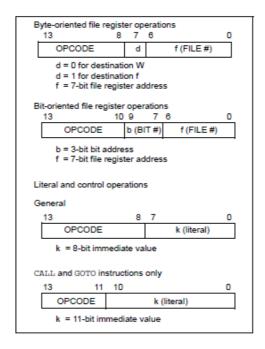

## II.3.4. Jeu d'instructions :

Les PICs sont conçus selon une architecture RISC. Programmer avec un nombre d'instructions réduit permet de limiter la taille de leur codage et donc de la place mémoire et du temps d'exécution.

## II.3.4.a. Format général:

Toutes les instructions sont codées sur 14 bits. Elles sont regroupées en trois grands types (Figure [II.7]) :

- Instructions orientées octets ;

- Instructions orientées bits ;

- Instructions de contrôle.

Le registre de travail W joue un rôle particulier dans un grand nombre d'instructions.

Figure [II.7]: Format générale des instructions.

## II.3.4.b. Exemple d'instruction – le transfert :

Trois instructions de transfert sont disponibles sur le PIC 16F84. La Figure [II.8] permet de transférer le contenu du registre W dans un registre f. On peut noter la valeur du bit 7 à 1 et les bits 0 à 6 donnant le registre concerné.

Figure [II.8]: transfer du registre W dans le registre f.

La Figure [II.9] permet de transférer une donnée contenue dans un registre W vers le registre f. Dans ce cas, l'intérêt est de positionner le bit Z. On peut noter ici le bit 7 qui prend la valeur « d » fournie dans le code de l'instruction pour choisir la destination : W ou f.

**Figure [II.9] :** Transfer du contenu de registre W dans le registre f.

La figure [II.10] présente une instruction qui permet de charger une constante dans le registre W. Ici, la valeur à charger est donnée sur 8 bits, le bit 7 n'étant pas utile puisque le code de l'instruction dit que la valeur est à charger dans le registre W.

Figure [II.10]: Transfer d'une constante dans le registre W.

## II.3.4.c. Liste des instructions : [12]

La figure [II.11] donne la liste de toutes les instructions du PIC 16F84.

| Mnemonic,<br>Operands               |                                        | Description.                 | Cycles  | 14-Bit Opcode |      |      |      | Status   | Notes |  |

|-------------------------------------|----------------------------------------|------------------------------|---------|---------------|------|------|------|----------|-------|--|

|                                     |                                        | Description                  | Cycles  | MSb           |      |      | LSb  | Affected | Notes |  |

|                                     | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |         |               |      |      |      |          |       |  |

| ADDWF                               | f, d                                   | Add W and f                  | 1       | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |  |

| ANDWF                               | f, d                                   | AND W with f                 | 1       | 00            | 0101 | dfff | TTTT | Z        | 1,2   |  |

| CLRF                                | f                                      | Clear f                      | 1       | 00            | 0001 | lfff | ffff | Z        | 2     |  |

| CLRW                                | -                                      | Clear W                      | 1       | 00            | 0001 | 0xxx | XXXX | Z        |       |  |

| COMF                                | f, d                                   | Complement f                 | 1       | 00            | 1001 | dfff | ffff | Z        | 1,2   |  |

| DECF                                | f, d                                   | Decrement f                  | 1       | 00            | 0011 | dfff | ffff | Z        | 1,2   |  |

| DECFSZ                              | f, d                                   | Decrement f, Skip if 0       | 1 (2)   | 00            | 1011 | dfff | ffff |          | 1,2,3 |  |

| INCF                                | t, d                                   | Increment f                  | 1       | 00            | 1010 | dfff | ffff | 2        | 1,2   |  |

| INCFSZ                              | f, d                                   | Increment f, Skip if 0       | 1 (2)   | 00            | 1111 | dfff | TTTT |          | 1,2,3 |  |

| IORWF                               | f, d                                   | Inclusive OR W with f        | 1       | 00            | 0100 | dfff | ffff | Z        | 1,2   |  |

| MOVF                                | f, d                                   | Move f                       | 1       | 00            | 1000 | dfff | ffff | Z        | 1,2   |  |

| MOVWF                               | f                                      | Move W to f                  | 1       | 00            | 0000 | lfff | ffff |          |       |  |

| NOP                                 | -                                      | No Operation                 | 1       | 00            | 0000 | 0xx0 | 0000 |          |       |  |

| RLF                                 | f, d                                   | Rotate Left f through Carry  | 1       | 00            | 1101 | dfff | ffff | С        | 1,2   |  |

| RRF                                 | f, d                                   | Rotate Right f through Carry | 1       | 00            | 1100 | dfff | 1111 | C        | 1,2   |  |

| SUBWF                               | f, d                                   | Subtract W from f            | 1       | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |  |

| SWAPF                               | f, d                                   | Swap nibbles in f            | 1       | 00            | 1110 | dfff | ffff |          | 1,2   |  |

| XORWF                               | f, d                                   | Exclusive OR W with f        | 1       | 00            | 0110 | dfff | ffff | Z        | 1,2   |  |

|                                     |                                        | BIT-ORIENTED FILE REGIST     | ER OPER | MOITAS        | NS.  |      |      |          |       |  |

| BCF                                 | f, b                                   | Bit Clear f                  | 1       | 01            |      | bfff |      |          | 1,2   |  |

| BSF                                 | f, b                                   | Bit Set f                    | 1       | 01            |      | bfff |      |          | 1,2   |  |

| BTFSC                               | f, b                                   | Bit Test f, Skip if Clear    | 1 (2)   | 01            | 10bb | bfff | ffff |          | 3     |  |

| BTFSS                               | f, b                                   | Bit Test f, Skip if Set      | 1 (2)   | 01            | 11bb | bfff | ffff |          | 3     |  |

|                                     |                                        | LITERAL AND CONTROL          | OPERAT  | ONS           |      |      |      |          |       |  |

| ADDLW                               | k                                      | Add literal and W            | 1       | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |  |

| ANDLW                               | k                                      | AND literal with W           | 1       | 11            |      | kkkk |      | Z        |       |  |

| CALL                                | k                                      | Call subroutine              | 2       | 10            | 0kkk | kkkk | kkkk |          |       |  |

| CLRWDT                              | -                                      | Clear Watchdog Timer         | 1       | 00            | 0000 | 0110 | 0100 | TO,PD    |       |  |

| GOTO                                | k                                      | Go to address                | 2       | 10            |      | kkkk |      |          |       |  |

| IORLW                               | k                                      | Inclusive OR literal with W  | 1       | 11            | 1000 | kkkk | kkkk | Z        |       |  |

| MOVLW                               | k                                      | Move literal to W            | 1       | 11            | 00xx | kkkk | kkkk |          |       |  |

| RETFIE                              | -                                      | Return from interrupt        | 2       | 00            | 0000 |      | 1001 |          |       |  |

| RETLW                               | k                                      | Return with literal in W     | 2       | 11            | 01xx | kkkk |      |          |       |  |

| RETURN                              | -                                      | Return from Subroutine       | 2       | 00            | 0000 | 0000 | 1000 |          |       |  |

| SLEEP                               | -                                      | Go into standby mode         | 1       | 00            | 0000 | 0110 | 0011 | TO,PD    |       |  |